A migrazione di u centru di dati à DDR5 pò esse più impurtante chè altre aghjurnamenti.Tuttavia, assai persone pensanu vagamente chì DDR5 hè solu una transizione per rimpiazzà completamente DDR4.I prucessori cambianu inevitabbilmente cù l'arrivu di DDR5, è anu avutu qualchì novumemoriainterfacce, cum'è era u casu cù e generazioni precedenti di aghjurnamenti DRAM da SDRAM àDDR4.

Tuttavia, DDR5 ùn hè micca solu un cambiamentu di l'interfaccia, hè cambiatu u cuncettu di sistema di memoria di processore.In fatti, i cambiamenti à DDR5 pò esse abbastanza per ghjustificà un aghjurnamentu à una piattaforma di servitore compatible.

Perchè sceglie una nova interfaccia di memoria?

I prublemi di l'informatica sò diventati più cumplessi da l'avventu di l'urdinatori, è sta crescita inevitabbile hà guidatu l'evoluzione in a forma di un numeru più grande di servitori, capacità di memoria è di almacenamento sempre crescente, è velocità di clock di u processore è cunti di core più elevate, ma ancu guidanu cambiamenti architetturali. , cumpresa l'adopzione recente di tecniche AI disaggregate è implementate.

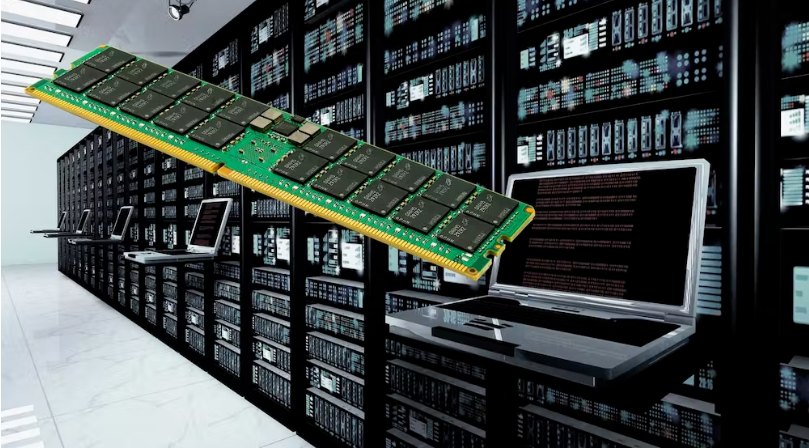

Qualchidunu puderia pensà chì questi sò tutti accaduti in tandem perchè tutti i numeri crescenu.In ogni casu, mentri u numeru di nuclei di processore hè aumentatu, a larghezza di banda DDR ùn hà micca seguitu u ritmu, cusì a larghezza di banda per core hè in realtà diminuite.

Siccomu i setti di dati sò stati in espansione, soprattuttu per HPC, ghjochi, codificazione video, ragiunamentu di l'apprendimentu di machine, analisi di big data, è basa di dati, anche se a larghezza di banda di trasferimenti di memoria pò esse migliurata aghjunghjendu più canali di memoria à u CPU, Ma questu cunsuma più putere. .U cuntu di pin di u processatore limita ancu a sustenibilità di questu approcciu, è u numeru di canali ùn pò micca cresce per sempre.

Certi appricazzioni, in particulare i sottosistemi high-core, cum'è GPU è processori AI specializati, utilizanu un tipu di memoria di larghezza di banda alta (HBM).A tecnulugia gestisce e dati da chip DRAM impilati à u processore per via di memoria di 1024-bit, facendu una grande soluzione per applicazioni intensive di memoria cum'è AI.In queste applicazioni, u processatore è a memoria deve esse u più vicinu pussibule per furnisce trasferimenti veloci.In ogni casu, hè ancu più caru, è i chips ùn ponu micca adatti à moduli rimpiazzabili / aghjurnà.

È a memoria DDR5, chì hà cuminciatu à esse largamente sparghje questu annu, hè pensata per migliurà a larghezza di banda di u canali trà u processore è a memoria, mentre sustene l'aghjurnamentu.

Larghezza di banda è latenza

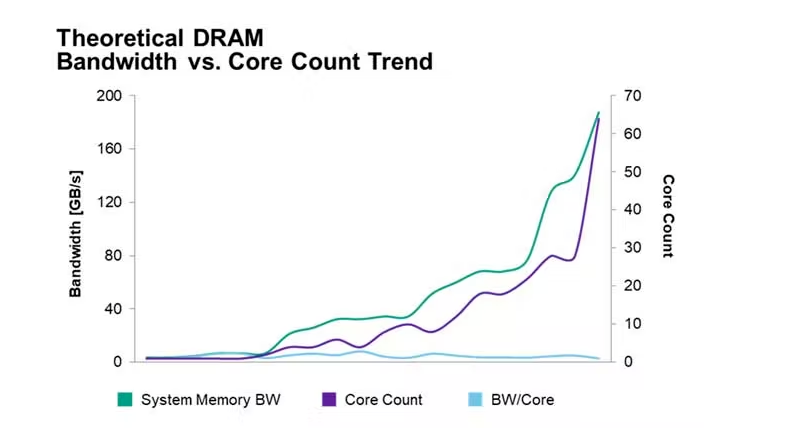

A rata di trasferimentu di DDR5 hè più veloce di quella di qualsiasi generazione precedente di DDR, in fattu, paragunatu à DDR4, a rata di trasferimentu di DDR5 hè più di u doppiu.DDR5 introduce ancu cambiamenti architetturali supplementari per attivà u rendiment à questi tassi di trasferimentu annantu à guadagni simplici è migliurà l'efficienza di bus di dati osservata.

Inoltre, a durata di u burst hè stata radduppiata da BL8 à BL16, chì permette à ogni modulu di avè dui sub-canali indipendenti è essenzialmente duppià i canali dispunibili in u sistema.Micca solu ottene velocità di trasferimentu più altu, ma ancu ottene un canale di memoria ricustruita chì supera DDR4 ancu senza tassi di trasferimentu più altu.

I prucessi intensivi di memoria vederanu un grande impulso da a transizione à DDR5, è assai di i carichi di travagliu intensivi di dati d'oghje, in particulare AI, basa di dati, è trasfurmazioni di transazzione in linea (OLTP), si adattanu à sta descrizzione.

A velocità di trasmissione hè ancu assai impurtante.L'attuale gamma di velocità di memoria DDR5 hè 4800 ~ 6400MT/s.Quandu a tecnulugia matura, a velocità di trasmissione hè prevista per esse più altu.

Cunsumu d'energia

DDR5 usa una tensione più bassa cà DDR4, vale à dì 1.1V invece di 1.2V.Mentre chì una differenza di 8% ùn pò micca sona assai, a diffarenza diventa apparente quandu sò quadrate per calculà u rapportu di cunsumu di energia, vale à dì 1,1² / 1,2² = 85%, chì si traduce in un risparmiu di 15% nantu à e bollette di l'electricità.

I cambiamenti architetturali introdutti da DDR5 ottimisanu l'efficienza di a larghezza di banda è i tassi di trasferimentu più altu, in ogni modu, questi numeri sò difficiuli di quantificà senza misurà l'ambiente d'applicazione esatta in quale a tecnulugia hè aduprata.Ma di novu, per via di l'architettura mejorata è di i tassi di trasferimentu più altu, l'utilizatore finale perciverà una migliione di energia per bit di dati.

Inoltre, u modulu DIMM pò ancu aghjustà a tensione da ellu stessu, chì pò riduce a necessità di aghjustamentu di l'alimentazione di a scheda madre, fornendu cusì effetti supplementari di risparmiu d'energia.

Per i centri di dati, quantu putere cunsumu un servitore è quantu i costi di rinfrescamentu sò preoccupati, è quandu questi fattori sò cunsiderati, DDR5 cum'è un modulu più efficiente in energia pò certamente esse un mutivu per aghjurnà.

Correzione di errore

DDR5 incorpora ancu a correzione d'errore in chip, è cum'è i prucessi DRAM cuntinueghjanu à riduzzione, parechji utilizatori sò preoccupati di aumentà a rata di errore di un bit è l'integrità di e dati in generale.

Per l'applicazioni di u servitore, l'ECC on-chip corregge l'errori di un bit durante i cumandamenti di lettura prima di emette dati da DDR5.Questu scarica una parte di a carica ECC da l'algoritmu di correzione di u sistema à a DRAM per riduce a carica di u sistema.

DDR5 introduce ancu a verificazione di l'errore è a sanitizazione, è se attivatu, i dispositi DRAM leghjeranu e dati internu è scriveranu dati curretti.

Riassume

Mentre chì l'interfaccia DRAM ùn hè di solitu micca u primu fattore chì un centru di dati cunsidereghja quandu implementa un aghjurnamentu, DDR5 meriteghja un sguardu più attentu, postu chì a tecnulugia prumette di risparmià energia mentre migliurà assai u rendiment.

DDR5 hè una tecnulugia abilitante chì aiuta i primi aduttatori à migrà grazia à u centru di dati cumpusibile è scalabile di u futuru.I dirigenti di l'IT è di l'imprese anu da valutà DDR5 è determinà cumu è quandu migrare da DDR4 à DDR5 per cumpletà i so piani di trasfurmazioni di u centru di dati.

Tempu di post: Dec-15-2022